1. Úvod

Ladiace funkcie sú používané hostiteľom ladenia (debuggerom) pokiaľ je pripojený k MCU STM32F4xx v režime ladenia.

Pre ladenie sú k dispozícii dve rozhrania:

- ladiaci port Serial Wire (sériová linka)

- ladiaci port JTAG

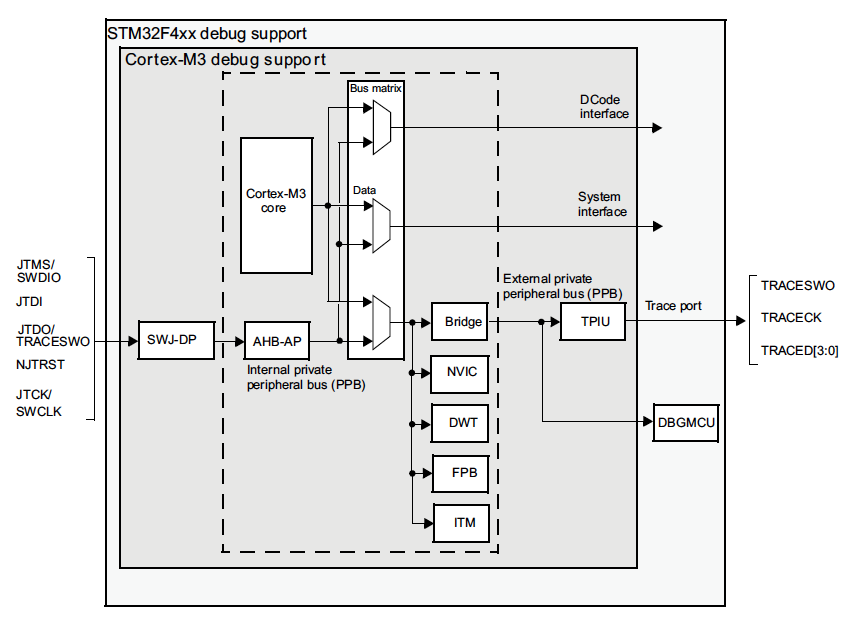

Obrázok 1: Blokový diagram podpory ladenia pre STM32 a CortexTM-M4F.

Jadro ARM CortexTM-M4F poskytuje podporu ladenia priamo na čipe. Skladá sa z:

- SWJ-DP: ladiaci port Serial Wire JTAG (DP – debug port)

- AHP-AP: prístupový port AHB

- ITM: Instumentation Trace Macrocell (makrobunka sledovania nástrojového vybavenia)

- FPB: Flash Patch Breakpoint

- DWT: Data Watchpoint Trigger (spúšť pre sledovanie prístupu k dátam)

- TPUI: Trace Port Unit Interface (jednotka rozhrania sledovania portu) – dostupná pri väčších púzdrach, kde sú namapované odpovedajúce piny

- ETM: Embedded Trace Macrocell (vstavaná makrobunka sledovania) - dostupná pri väčších púzdrach, kde sú namapované odpovedajúce piny. Obsahuje tiež ladiace funkcie určené pre STM32F4xx

- Flexibilné priradenie ladiacich portov

- Ladiaci box MCU (podpora pre režimy nízkej spotreby, riadenie hodín periférií, atď.)

2.Ladiaci port SWJ (Serial Wire a JTAG)

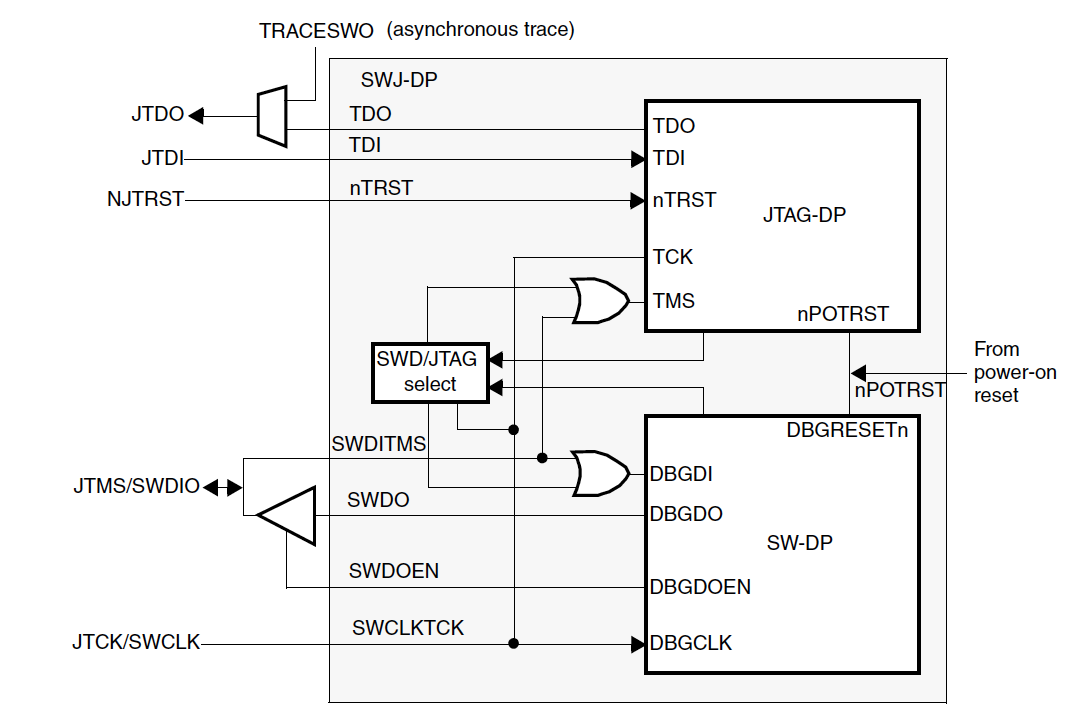

Jadro STM32F4xx má v sebe integrované rozhranie pre ladenie Serial Wire / JTAG (SWJ-DP). Je to ARMový štandartný CoreSight ladiaci port, ktorý kombinuje rozhrania JTAG-DP (5 pinov) a SW-DP (2 piny).

- ladiaci port JTAG (JTAG-DP) poskytuje 5-pinové štandartné JTAG rozhranie k portu AHP-AP.

- Ladiaci port Serial Wire (SW-DP) poskytuje 2-pinové rozhranie (hodiny + dáta) k portu AHP-AP.

V SWJ-DP sú dva piny z SW-DP multiplexované s niektorými z piatich pinov JTAG-DP.

Obrázok 2: Znázornenie ako je asynchrónny TRACE výstup (TRACESWO) multiplexovaný s TDO. To znamená, že asynchrónne trasovanie môže byť použité jedine s SW-DP a nie s JTAG-DP.

2.1 Mechanizmus výberu JTAG-DP alebo SW-DP

Štandartne je aktívny ladiaci port JTAG. Ak chce hostiteľ ladenia (debugger) prepnúť na SW-DP, tak musí poskytnúť špeciálnu JTAG sekvenciu na pinoch TMS / TCK (respektíve mapovaných ako SWDIO a SWCLK), ktorá zakáže SW-JTAG a povolí SW-DP. Týmto spôsobom je možné aktivovať SW-DP použitím len dvoch pinov SWCLK a SWDIO.

Sekvencia vyzerá takto:

- Poslať viac ako 50 cyklov TCK pri TMS (SWDIO) = 1

- Poslať 16-bitovú sekvenciu na TMS (SWDIO) = 0111100111100111 (MSB sa vysiela ako prvé)

- Poslať viac ako 50 cyklov TCK pri TMS (SWDIO) = 1

3. Piny ladiaceho portu

STM32F4xx sú dostupné v rôznych púzdrach s rôznym počtom dostupných pinov. V dôsledku toho sa môžu niektoré funkcie vzhľadom na dostupnosť, resp. nedostupnosť pinov líšiť medzi púzdrami.

3.1 Piny ladiaceho portu SWJ.

Päť pinov je použitých v STM32F4xx ako výstup pre SWJ-DP. Použité sú ako alternatíva k univerzálnym V/V (vstupno / výstupným) pinom - GPIO. Tieto piny sú dostupné vo všetkých púzdrach.

| meno pinu SWJ-DP | ladiaci port JTAG | ladiaci port SW | odpovedajúci | ||

| typ | popis | typ | popis | pin | |

| JTMS / SWDIO | vstup | výber módu JTAG | vstup / výstup | vstupno/výstupné dáta pre Serial Wire | PA13 |

| JTCK / SWCLK | vstup | hodiny JTAG | vstup | hodiny pre Serial Wire | PA14 |

| JTDI | vstup | vstupné dáta JTAG | - | PA15 | |

| JTDO / TRACESWO | výstup | výstupné dáta JTAG | - | TRACESWO ak je povolené asynchonné trasovanie | PB3 |

| NJTRST | vstup | nReset JTAG | - | PB4 | |

Tabuľka 1: Piny ladiaceho portu SWJ.

3.2 Flexibilné priraďovanie pinov SWJ-DP

Po resete (SYSRESETn alebo PORESETn) je všetkých päť pinov použitých pre SWJ-DP priradených ako vyhradené piny okamžite použiteľné pre hostiteľa ladenia (všimnite si, že trasovacie výstupy nie sú obsadené s výnimkou, kedy sú explicitne naprogravané hostiteľom ladenia). Avšak STM32F4xx ponúka možnosť zakázať niektoré, alebo aj všetky piny z SWJ-DP portu a tak ich uvoľniť pre použitie ako univerzálnych V/V pinov (GPIO).

| dostupné ladiace porty | priradenie IO pinov | ||||

| PA13 | PA14 | PA15 | PB3 | PB4 | |

| JTMS | JTCK | JTDI | JTO | NJTRST | |

| SWDIO | SWCLK | ||||

| plný SWJ (JTAG-DP + SW-DP) s NJTRST | X | X | X | X | X |

| plný SWJ (JTAG-DP + SW-DP) bez NJTRST | X | X | X | X | |

| zakázaný JTAG-DP a povolený SW-DP | X | X | |||

| zakázaný JTAG-DP a zakázaný SW-DP | uvoľnené | ||||

Tabuľka 2: Flexibilné priraďovanie pinov SWJ-DP.

3.3 Vnútorné pull-up a pull-down rezistory na JTAG pinoch

Je potrebné zabezpečiť, aby vstupné piny JTAG rozhrania neboli plávajúce, pretože sú priamo pripojené ku klopným obvodom, ktoré ovládajú funkcie ladenia. Zvláštna pozornosť musí byť venovaná pinu SWCLK / TCK, ktorý je priamo pripojený na hodiny niektorých z týchto klopných obvodov.

Aby sa zabránilo vzniku nekontrolovanej (zakázanej) úrovne, tak procesor má vstavané interné pull-up a pull-down rezistory na vstupných JTAG pinoch

- NJTRST: vnútorný pull-up

- JTDI: vnútorný pull-up

- JTMS / SWDIO: vnútorný pull-up

- TCK / SWCLK: vnútorný pull-down

Akonáhle sa JTAG port uvoľní užívateľským softvérom, tak GPIO ovládač opäť prevezme kontrolu nad týmito pinmy. Ovládač GPIO dá piny do nasledujúceho východzieho stavu

- NJTRST: AF vstup s pull-up

- JTDI: AF vstup s pull-up

- JTMS / SWDIO: AF vstup s pull-up

- JTCK / SWCLK: AF vstup s pull-down

- JTDO: AF plávajúci výstup

Softvér môže potom používať tieto V/V piny ako štandartné univerzálne V/V piny (GPIO).

3.4 Používanie Serial Wire a uvoľnenie nepoužitých ladiacich pinov ako GPIO

Pre použitie ladiaceho portu Serial Wire a uvoľnenie niektorých pinov ako GPIO (PA15, PB3 a PB4) musí užívateľský softvér zmeniť konfiguračný mód v GPIO_MODER registry . Toto uvoľní PA15, PB3 a PB4, ktoré sa od tohto momentu stanú dostupné ako univerzálne V/V piny (GPIO).

Pokiaľ ladíme, tak hostiteľská strana musí vykonať/splniť tieto úkony:

- Počas systémového resetu sú všetky SWJ piny priradené ladiacej funkcii (JTAG-DP + SW-DP)

- Počas systémového resetu hostiteľ ladenia pošle na JTAG rozhranie sekvenciu, ktorá prepne z JTAG-DP na SW-DP.

- Stále počas systémového resetu debugger nastaví breakpoint (miesto prerušenia) na vektor resetu.

- Systémový reset je uvoľnený a jadro zastavené.

- Celá komunikácia ladenia je od tohto momentu vykonávaná použitím SW-DP. Ostatné JTAG piny môžu byť teraz užívateľkým softvérom nakonfigurované ako GPIO.

Poznámka:

Netreba zabúdať na to, že ladiace piny sú najprv nakonfigurované ako vstupné piny s pull-up (nTRST, TMS, TDI), alebo vstupý pin s pull-down (TCK), alebo ako trojstavový výstup (TDO) určitú dobu po resete až do okamihu, kedy ich užívateľský softvér uvoľní.

Pokiaľ sú ladiace piny (JTAG, SW, alebo TRACE) mapované ako ladiace, tak zmena v odpovedajúcom IO registri IOPORT neafektuje tieto piny.